## Билет 32. Архитектурные особенности современных микропроцессоров.

## 1. Основные понятия.

**Микропроцессорная техника (МПТ)** включает технические и программные средства, используемые для построения различных микропроцессорных систем, устройств и персональных микроЭВМ.

**Микропроцессорная система (МПС)** представляет собой функционально законченное изделие, состоящее из одного или нескольких устройств, главным образом микропроцессорных: микропроцессора и/или микроконтроллера.

**Микропроцессорное устройство (МПУ)** представляет собой функционально и конструктивно законченное изделие, состоящее из нескольких микросхем, в состав которых входит микропроцессор; оно предназначено для выполнения определенного набора функций: получение, обработка, передача, преобразование информации и управление.

**Микропроцессором (МП)** называется программно-управляемое устройство, осуществляющее процесс цифровой обработки информации и управления им и построенное, как правило, на одной БИС.

Разные МП или МК объединяют в семейства как технология «микроядра», в качестве которого выступает процессорное ядро, взаимодействующее с периферийными устройствами различной номенклатуры, так и принципы, свойственные открытым системам: совместимость (compatibility), масштабируемость (scalability), переносимость (portability) и взаимодействие приложений (introperability).

Выпускаемые микропроцессоры делятся на отдельные классы в соответствии с их архитектурой, структурой и функциональным назначением. Основными направлениями развития микропроцессоров является увеличение их производительности и расширение функциональных возможностей, что достигается как повышением уровня микроэлектронной технологии, используемой для производства микропроцессоров, так и применением новых архитектурных и структурных вариантов их реализации.

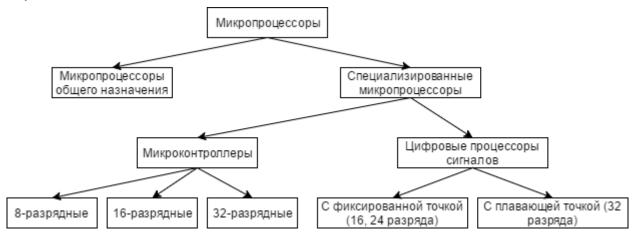

На рисунке приведена классификация современных микропроцессоров по функциональному признаку.

Классификация современных микропроцессоров по функциональному признаку

**Микропроцессоры общего назначения** предназначены для решения широкого круга задач обработки разнообразной информации. Их основной областью использования являются персональные компьютеры, рабочие станции, серверы и другие цифровые системы массового применения.

Специализированные микропроцессоры ориентированы на решение специфичных задач управления различными объектами. Содержат дополнительные микросхемы (интерфейсы), обеспечивающие специализированное применение. Имеют особую конструкцию, повышенную надежность.

**Микроконтроллеры** являются специализированными микропроцессорами, которые ориентированы на реализацию устройств управления, встраиваемых в разнообразную аппаратуру. Характерной особенностью структуры микроконтроллеров является размещение на одном кристалле с центральным процессором внутренней памяти и большого набора периферийных устройств.

**Цифровые процессоры сигналов (ЦПС)** представляют класс специализированных микропроцессоров, ориентированных на цифровую обработку поступающих аналоговых сигналов. Специфической особенностью алгоритмов обработки аналоговых сигналов является необходимость последовательного выполнения ряда команд умножения-сложения с накоплением промежуточного результата в регистре-аккумуляторе. Поэтому архитектура ЦПС ориентирована на реализацию быстрого выполнения операций такого рода. Набор команд этих процессоров содержит специальные команды MAC (Multiplication with Accumlation), реализующие эти операции.

**Архитектурой процессора** называется комплекс его аппаратных и программных средств, предоставляемых пользователю. В это общее понятие входит набор программно-доступных регистров и исполнительных (операционных) устройств, система основных команд и способов адресации, объем и структура адресуемой памяти, виды и способы обработки прерываний.

При описании архитектуры и функционирования процессора обычно используется его представление совокупности программно-доступных виде регистров, образующих регистровую или программную модель. В этих регистрах содержатся обрабатываемые данные (операнды) и управляющая информация. Соответственно, в регистровую модель входит группа регистров общего назначения, служащих хранения ДЛЯ группа служебных регистров, обеспечивающих управление выполнением программы и режимом работы процессора, организацию обращения к памяти (защита памяти, сегментная и страничная организация и др.).

Регистры общего назначения образуют РЗУ - внутреннюю регистровую память процессора. Состав и количество служебных регистров определяется архитектурой микропроцессора. Обычно в их состав входят:

- программный счетчик PC (или CS + IP в архитектуре микропроцессоров Intel);

- регистр состояния SR (или EFLAGS);

- регистры управления режимом работы процессора CR (Control Register);

- регистры, реализующие сегментную и страничную организацию памяти;

- регистры, обеспечивающие отладку программ и тестирование процессора.

Кроме того, различные модели микропроцессоров содержат ряд других специализированных регистров.

Состав устройств и блоков, входящих в структуру микропроцессора, и реализуемые механизмы их взаимодействия определяются функциональным назначением и областью применения микропроцессора.

Архитектура и структура микропроцессора тесно взаимосвязаны. Реализация тех или иных архитектурных особенностей требует введения в структуру микропроцессора необходимых аппаратных средств (устройств и блоков) и обеспечения соответствующих механизмов их совместного функционирования. В современных микропроцессорах реализуются следующие варианты архитектур.

CISC (Complex Instruction Set Computer) - архитектура реализована во многих типах микропроцессоров, выполняющих большой набор разноформатных команд с использованием многочисленных способов адресации. Они выполняют более 200 команд разной степени сложности, которые имеют размер от 1 до 15 байт и обеспечивают более 10 различных способов адресации. Такое большое многообразие выполняемых команд и способов адресации позволяет программисту реализовать наиболее эффективные алгоритмы решения различных задач.

**RISC (Reduced Instruction Set Computer)** - архитектура отличается использованием ограниченного набора команд фиксированного формата. Современные RISC-процессоры обычно реализуют около 100 команд, имеющих фиксированный формат длиной 4 байта. Также значительно

сокращается число используемых способов адресации. Обычно в RISC-процессорах все команды обработки данных выполняются только с регистровой или непосредственной адресацией.

**VLIW** (Very Large Instruction Word) - архитектура появилась относительно недавно - в 1990-х годах. Ее особенностью является использование очень длинных команд (до 128 бит и более), отдельные поля которых содержат коды, обеспечивающие выполнение различных операций. Таким образом, одна команда вызывает выполнение сразу нескольких операций параллельно в различных операционных устройствах, входящих в структуру микропроцессора.

Кроме набора выполняемых команд и способов адресации важной архитектурной особенностью микропроцессоров является используемый вариант реализации памяти и организация выборки команд и данных. По этим признакам различаются процессоры с Принстонской и Гарвардской архитектурой.

**Принстонская архитектура**, которая часто называется архитектурой Фон-Неймана, характеризуется использованием общей оперативной памяти для хранения программ, данных, а также для организации стека. Для обращения к этой памяти используется общая системная шина, по которой в процессор поступают и команды, и данные. Эта архитектура имеет ряд важных достоинств. Наличие общей памяти позволяет оперативно перераспределять ее объем для хранения отдельных массивов команд, данных и реализации стека в зависимости от решаемых задач.

Гарвардская архитектура характеризуется физическим разделением памяти команд (программ) и памяти данных. В ее оригинальном варианте использовался также отдельный стек для хранения содержимого программного счетчика, который обеспечивал возможности выполнения вложенных подпрограмм. Каждая память соединяется с процессором отдельной шиной, что позволяет одновременно с чтением-записью данных при выполнении текущей команды производить выборку и декодирование следующей команды. Благодаря такому разделению потоков команд и данных и совмещению операций их выборки реализуется более высокая производительность, чем при использовании Принстонской архитектуры.

## 2. Архитектурные особенности

Рассматриваются на основе изучения семейства МП Intel x86.

| Архитектурная     | Описание                                               | Где впервые    |

|-------------------|--------------------------------------------------------|----------------|

| особенность       |                                                        | появилась      |

| Многозадачность   | Возможность работы в одном из двух режимов: реальном   | Intel 80286    |

|                   | (real) и защищенном (protected). В реальном режиме     |                |

|                   | возможно выполнение только одной программы. Адресация  |                |

|                   | оперативной памяти без специальных драйверов           |                |

|                   | ограничивается 1Мб. В защищенном (protected) режиме    |                |

|                   | обеспечивается выполнение сразу нескольких программ за |                |

|                   | счет переключения между задачами («переключение        |                |

|                   | контекста процессора»). Адресация основной памяти      |                |

|                   | расширена до 4 ГБ (в последних МП – до 100 ГБ).        |                |

| Поддержка системы | Дальнейшее развитие принципа многозадачности,          | Intel 80386    |

| виртуальных машин | возможность моделирования в одном МП работу нескольких |                |

|                   | компьютеров, управляемых разными ОС.                   |                |

| Конвейерная       | Одновременное выполнение разных тактов                 | Intel 80286    |

| обработка команд  | последовательных команд в разных частях МП с           |                |

|                   | непосредственной передачей результатов выполнения из   |                |

|                   | одной части МП в другую. Позволяло достигнуть          |                |

|                   | пятикратного увеличения производительности МП.         |                |

| Кэширование       | Использование высокоскоростного буфера для обмена      | Intel i386SLC, |

| данных            | данными между микропроцессорной памятью (регистрами    | Intel i486     |

|                   | МП) и основной памятью ЭВМ. В кэш-память заранее       | Многоуровнево  |

|                   | копируются те участки памяти, с которыми собирается    | е кэширование  |

| Суперскалярная архитектура Суперскалярная архитектура с поддержкой внеочередного исполнения команд («динамическое исполнение») | работать МП. Управление процессом кэширования осуществляется кэш-контроллером и производится параллельно с работой центрального процессора. Современные ЭВМ имеют иерархически организованную кэш-память (до 3 уровней).  Наличие в микропроцессоре более 1 конвейера для выполнения команд (параллелизм на уровне инструкций).  Наличие в микропроцессоре более 1 конвейера для выполнения команд, а также специальных схем, позволяющих изменить изначальную последовательность выполнения команд (не нарушая смысла алгоритма) с целью параллельной загрузки всех конвейеров. | - Intel Pentium II  Intel Pentium Intel Pentium Pro                                                            |

|--------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| Гарвардская архитектура процессора Расширенный набор инструкций                                                                | В кэш-памяти 1 уровня предусмотрено разделение команд и данных, которые хранятся отдельно друг от друга для повышения эффективности обработки.  Новые команды, расширяющие базовый набор инструкций МП, для работы с мультимедийной информацией и одновременной однотипной обработки множественных данных.                                                                                                                                                                                                                                                                       | Intel Pentium Pro  Intel Pentium MMX, Intel Pentium III, Intel Pentium IV, Семейство Intel Core, Intel Core 2  |

| Гибридизация RISC и CISC архитектуры                                                                                           | Преобразование стандартных х86-инструкций в RISC-подобные команды фиксированной длины. Еще не выполненные команды записываются в кэш инструкций в том порядке, в котором они будут подаваться на исполняющие устройства (конвейеры) МП. В кэш-памяти может храниться до 12000 микрокоманд. Перевод инструкций формата х86 в микрокоманды ядра процессора происходит асинхронно с работой основных исполняющих устройств.                                                                                                                                                         | Intel Pentium IV                                                                                               |

| Технология одновременной многопоточности                                                                                       | Эмуляция двух логических исполняющих устройств на одном физическом с целью более эффективно исполнять параллельно запущенные потоки команд (параллелизм на уровне потоков).                                                                                                                                                                                                                                                                                                                                                                                                      | Intel Pentium IV<br>Hyper-<br>Threading                                                                        |

| Многоядерные<br>процессоры                                                                                                     | Объединение двух или более исполняющих устройств на одной ИС, действующих как единое устройство. Обычно имеют общий кэш и интерфейсную систему для связи с другими устройствами ЭВМ.                                                                                                                                                                                                                                                                                                                                                                                             | Процессоры семейства Intel Core (Intel Core Duo, Intel Core 2 Duo, Pentium Dual Core, Intel core 2 Quad и др.) |

| Технология автоматического увеличения тактовой частоты процессора                                                              | Для обеспечения дополнительной производительности и при условии соблюдения ограничений по мощности, температуре и току, процессор может автоматически «разгоняться», то есть увеличивать рабочую тактовую частоту всех своих ядер.                                                                                                                                                                                                                                                                                                                                               | Процессоры<br>Core i5, i7                                                                                      |